Юный техник - для умелых рук 1989-02, страница 16

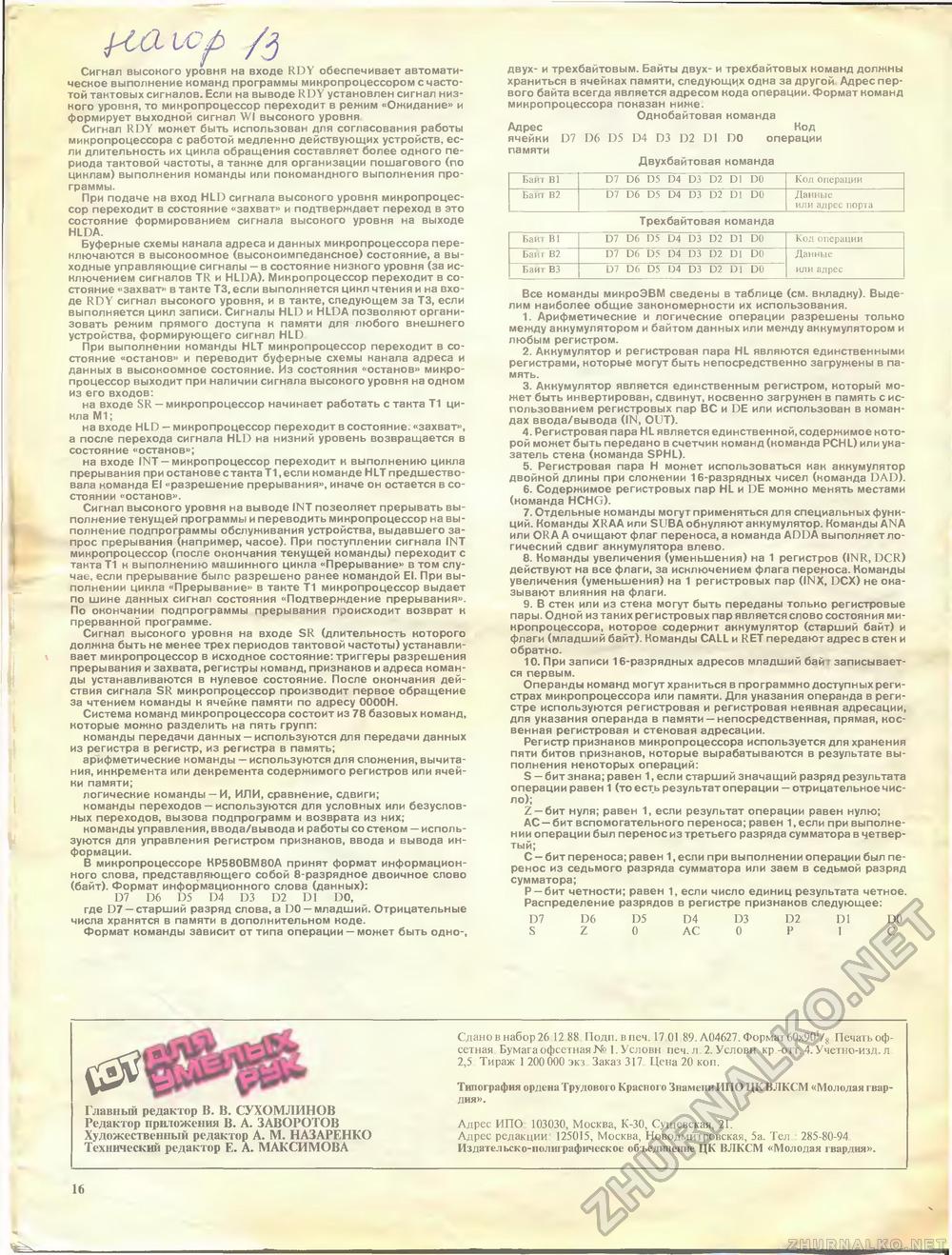

wpt lс ^ Сигнал высокого yp _,вня на входе RDY обеспечивает автоматическое выполнение команд программы ми юпроцессором с частотой тантовых сигналов. Если на выводе RDY установлен сигнал низкого урпвня, то микропроцесс р переходит в режим «Ожидание» и формирует выходной сигнал WI высокого уровня Сигнал RDY может ыть использован для согласования работы микропроцессора с работой медленно действуюи их устройств, если Диительносп их цикла обращения составляет более одного периода тактовой частоты, а также для организации пошагового (по циклам) выполнения команды или покомандного выполнения программы. При подаче на вход HLD сигнала высокого уровня микоопроцес соо . .ереходит в состояние «захват» и подтверждает переход в это с< стс 1ие формированием сигнала высокого уровня на выходе HLDA. Буферные схемы канала адреса и данных микр процессора пере-клк аю гея в высокоомное (высоноимпедансное) состояние, а выходные управляющие сигналы — в состояние низкого уровня (за исключением сигналов TR и HLDA). Микропроцессор переходит в состояние «захват» в такте ТЗ, если выполняется цикл чтения и на входе RDY сигнал высокого уровня, и в такте, следующем за ТЗ, если выполняется цикл записи. Сигналы HLD и HLDA позволяют организовать режим прямого доступа к памяти для любого внешнего устройства, формирующего сигнал HLD При выполнении команды HLT микропроцессор переходит в состояние «останов» и переводит буферные схемы канала адреса и данных в высоноомное состояние Из состояния «останов» микропроцессор выходит при наличии сигнала высокого уровня на одном из его входов: на входе SR - микропроцессор начинает работать с такта Т1 цикла М1 на в^оде HlD — микропрс ,эс :ор переходит в состояние «захват», а после перехода сигнала HLD на низний уровень возвращается в состояние «останов»; на входе INT — микропроцессо > переходит к вь олнению цикла прерывания при останове с такта Т1, если кома> де HLT предшествовал команда EI «разрешение прерывания», иначе он остается е состоянии «останов». Сигнал высокого уровня на выводе INT позволяет прерывать выполнение текущей программы и переводить микропроцессор на выполнение подпрограммы обслуживания устройства, выдавшего запрос прерывания например, часое). npi: поступлении сигнала INT мини I >цессор (после оьс нчания текущей команды) г,ереходит с такте! Т1 к выполнению машинного цикла «Прерывание» . и случае, если прерывание было разрешено ранее командой EI. При выполнении цикла «Прерывание» в такте Т1 микропроцессор выдает по шине данных сигнал состояния «Подтверждение прерывания». По оконча1.ии подпрограммы прерывания происходит возврат к прерванной программе. Сигн< к высокого уровня на входе SR (дл ельность которого должна быть не менее трех периодов тактовой частоты) устанавливает микропро дессор в исходное состояние, триггеры pi зрешения прерывания и захвата, регистры команд, npt знаков и адреса команды устанавливс >тся в нулевое состояние. После окончания действия сигнала SR микропроцессор производит п< ;ое обращение з чтением команды к ячейке памяти по адресу 0000Н. Система команд .микропроцессора состоит из 78 базовых команд, которые можно разделить на пять групп: команды передачи данных —используются для передачи данных из регистра в пегистр, из регистра в память; а >ифметические команды — используются для сложения, вычитания, инкремента или декремента содержимого регистров или ячейки памяти; логические команда— И, ИЛИ, сравнение, сдвиги; команды переходов — используются для условных или безусловных переходов, вызова подпрограмм и возврата из них. команды управления, ввода/вывода и работы со стеком — используются для управления регистром признаков, ввода и вывода информации. В микропроцессоре КР580ВМ8 принят формат информационного сг за, представляющего собой 8-разрядг в двоичное слово 'байт). Формат информационного слова (данных): D7 D6 D5 D4 D3 D2 D1 DO, где D7 —старший разряд слова, a DO —младший. Отрицательные числа хранятся в памяти в дополнительном коде Формат команды зависит от типа операции — может быть одно-, двух- и трехбайтовым, байты двух- и трехбайтовых команд должны храни I вся в ячейках памя-i и. следующих одна за другой. Адрес первого байта всегда является адресом кода операции. Формат команд микропроцессора показан i- иж4 Однобайтовая команда Адрес Код ячейки D7 D6 D5 D4 D3 D2 D1 DO операции памяти Двухбайтовая команда

Все команды микроЭВМ сведены в таблице (см. вкладку). Выделим наиболее общие закономерности их использования. 1 Арифметические и логические операции разрешены только между аккумулятором и байтом данных или между аккумулятором и люоым регистром. 2. Аккумулятор и регистровая пара HL являются единственными регистрами, которые могут быть непосредственно загружены в па мять. 3. Аккумулятор является единственным регистром, который может быть инвертирован, сдвину г,осе нно загружен в память с использованием pei рг >ix пар ВС и DE или использован в командах ввода/вывода (IN XT). 4. Регистровая пара HL является единственной, содерн мое которой может быть передано в счетчик команд (команда РСН L) или ука-зател з стека (команда SPHL). 5. Pei стоовая пара Н может использоваться как аккумуля р двойной длчны при сложении 16-разрядных чисел (команда DAD). 6. Соде^г регистровых nap Н_ и DE можно менять местами (коганда HCHG). 7 ~тчельнь к< ...анды могут применяться для специальных функций. Koi зы XRAA или SUbA обнуляют аккумут и э. Командь ,NA или OR/-. V очищают флаг переноса, а команда ADDA выполняет ло-гииеский сдвиг аккумуля! зпа влево. и. Команды увеличения (уменьшения) на 1 регистров (INR, DCR) действуют на все флаги з исключением флага n(.pi!ui Команды увеличения (уменьшения) на 1 регистровых пар (INX, DCX) не оказывают влияния на флаги. 9. В стек или из стека могут быть переданы только регистровые пары Одной из таких регистровых паря зляется ели огостоя иями-кроп|_ иессорэ, кото| с а содер ..лт к «улятор (старший байт) и фЖси (младший байт), "оманды CALL и RET передают адре : в стен и обрап ю 10. При записи 16-разрядных адресов младший байт записывается первым. Операнды команд могут хранитьо з программно доступных регистрах микропроцессора или памяти. Для указания оперг да в регистре используются регистровая и регистровая неявная адресации, для указания операнда в памяти — непосредственная, прягая, косвенная регистровая и стековая адресации. Регистр признаков микропроцессора используется для хранения пяти битов признаков, которые вырабатываются в результате выполнения некоторых операций: S —бит знака, равен 1 если старший значащий разряд результата о ~>рации равен 1 (то есть результат операции — отрицательноечис- Л т Z — бит нуля; равен 1 если результат операции равен нулю; АС —бит вспомогательного переноса; равен 1,если при выполнении операции был перенос из третьего разряда сумматора в четвертый; С — бит переноса; равен 1, если при выполнении операции был перенос из седьмого разряда сумматора или заем в седьмой разряд сумм: гора, Р —бит четности; равен 1, если число единиц результата четное. Распределение разрядов в регистре признаков следующее: D7 D6 D5 D4 D3 D2 D1 DO S Z О АС О Р 1 С лавный редактор В. В СУХ< -М НОВ Редактор риложения В. A. и. )Т ЧЬ Художественным реда* op А VI. 1AJAPE1 КО Т нический редактор Е. А. МАКСИМОВА Сдано в набор26 12 88 Па^1.впеч. 1/ 01 89 А04627. Формат60х90,/8 Печать оф-сеть я Бумага |фсетная№ 1. Усювн печ. л 2. Условн кр-отт. 4. Учетио-изд. л 2,5 Тираж 1 200 ООО эк Заказ 317 Цена 20 коп. Типография ордена Трудового Красного Знамени ИПО ЦК ВЛКСМ «Молодая гвардия». Адрес ИПО 103030, Лосква, К 30, Сущев«кая, 21. Адрес редакции 125015, Москва, Новодмитровская, 5а. Тел : 285-80-94 Издательско-полиграфическое объединение ЦК ВЛКСМ «Молодая гвардия». 16 |

|||||||||||||||||