Юный техник - для умелых рук 1989-11, страница 12

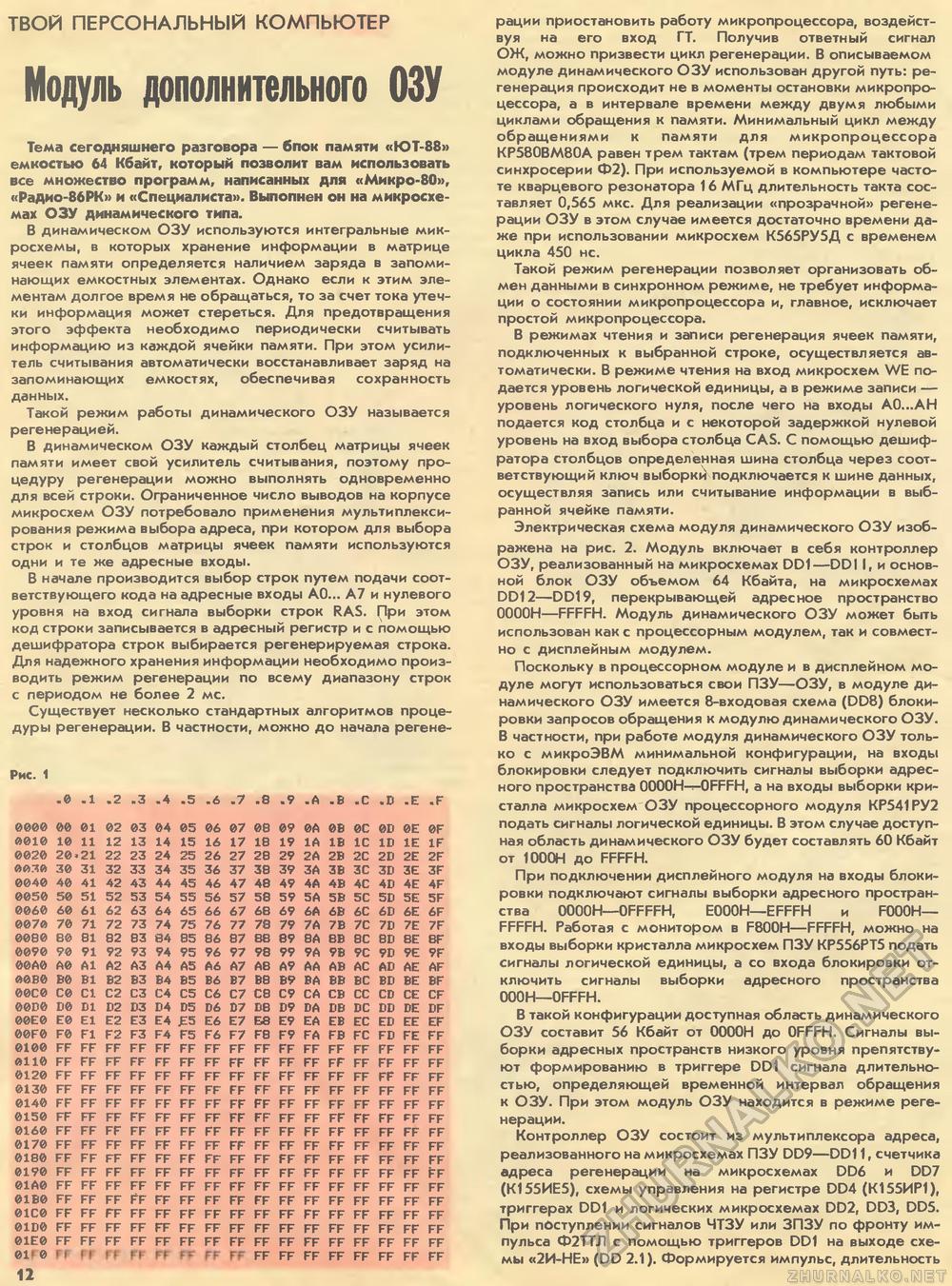

ТВОИ ПЕРСОНАЛЬНЫЙ КОМПЬЮТЕРМодуль дополнительного ОЗУ Тема сегодняшнего разговора — блок памяти «ЮТ-88» емкое ю 64 Кбайт, который позволит вам испол- зоват! все множество программ, написанных для «Микро-80», «РаДио-8бРК» и «Специалиста». Вылопньн он на микрос: -мах ОЗУ динамического типа. В динамическом ОЗУ используются интегральные микросхемы, в которых хранение информации в матрице ячеек памяти определяется наличием заряда в запоминающих емкостных элементах. Однако если к этим элементам долгое время не обращаться, то за счет тока утечки информация может стереться. Для предотвращения этого эффекта необходимо периодически считывать информацию из каждой ячейки памяти. При этом усилитель считывания автоматически восстанавливает заряд на запоминающих емкостях, обеспечивая сохранность данных. Такой режим работы динамического ОЗУ называется регенерацией. В динамическом ОЗУ каждый столбец матрицы ячеек памяти имеет свой усилитель считывания, поэтому процедуру регенерации можно выполнять одновременно для всей строки. Ограниченное число выводов на корпусе микросхем ОЗУ потребовало применения мультиплексирования режима выбора адреса, при котором для выбора строк и столбцов матрицы ячеек ..амяти используются одни и те же адресные входы. В начале производится выбор строк путем подачи соответствующего кодэ на адресные входы АО... А7 и нулевого уровня на вход сигнала выборки строк RAS. При этом код строки записывается в адресный регистр и с помощью дешифратора строк выбирается регенерируемая строка. Для надежного хранения информации необходимо производить режим регенерации по всему диапазону строк с периодом не более 2 мс. Существует несколько стандартных алгоритмов процедуры регенерации. В частности, можно до начала регене- .1 .2 .3 .4 .5 .6 .7 .8 .9 .А .6 .С .0 .Е .F 0020 20 ЙЙ.ЧЙ 30 0Я40 40 50 0070 70 0080 80 0096 90 0UA0 ни 00В0 В0 00( 0 С0 00D0 D0 00Е0 Е0 0OF0 F0 0100 FF 0110 FF 0120 FF 0130 FF 0140 FF 0150 FF 0160 FF 0170 FF 01в0 FF 0L90 FF 01А0 FF 01В0 FF 01С0 FF 01D0 FF 01Е0 FF 01 0 Р| 01 02 11 12 21 22 31 32 41 42 51 52 6i 62 71 72 81 82 91 92 А1 А2 В1 62 CI С2 D1 D2 El Е? F1 F2 FF FF FF FF PF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF .-F FF FF FF FF FF FF FF FF Ff ГГ 03 04 05 13 14 15 23 24 25 33 3'> 35 43 44 45 ■53 54 55 63 64 65 /3 7t 75 83 84 85 93 94 95 A3 А4 AS ВЗ В4 65 СЗ С4 С5 D3 D4 D5 ЕЗ Е4 £5 F3 F4 1-5 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF F F FF FF FF FF FF FF FF FF FF FF FF FF Е FF FF FF FT 06 07 08 16 1/ 18 26 27 28 36 37 38 46 47 41: 56 57 58 66 67 оП 76 77 7d 86 87 88 96 97 98 А6 А7 А8 В6 В7 В8 С6 С7 С8 D6 D7 U8 Е6 Е7 Б8 F6 F7 F8 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF 09 0A 19 1A 29 2A 39 ЗА 49 4A 59 5A 69 6A 79 7A 89 8A 99 91 A9 AA В? BA C9 CA D9 DA E9 EA F9 FA FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF 0B 0C IB 1С 2B 2C 3B 3C 4B 4C 5B 5C 6B 6C 7B 7C 8B 8C 9B 9C AB AC BB ВС CB CC DB DC EB EC KB FC FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF 0D 0E 0F ID IE IF 2D 2E 2F 3D 3E 3F 4D 4E 5D 5E 5F 6D 6E 6F 7D 7E 7F 8D 8E 8F 9D 9E 9F AD AE AF BD BE BF CD CE CF DD DE DF ED EE EF FD FE FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF 12 рац.чи приостановить работу микропроцессора, воздействуя на его вход ГТ. Получив ответный сигнал ОЖ, можно призвести цикл регенерации. В описываемом модуле динамического ОЗУ использован другой путь: регенерация происходит не в моменты остановки микропроцессора, а в интервале времени межд/ двумя любыми циклами обращения к памяти. Минимальный цикл между обращениями к памяти для микропроцессора KP5BUBM80A равен трем тактам (трем периодам тактовой синхросерии Ф2). При используемой в компьютере частоте кварцевого резонатора 16 МГц длительность такта составляет 0,565 мкс. Для реализации «прозрачной» регенерации ОЗУ в этом случае имеется достаточно времени даже при использовании микросхем К565РУ5Д с временем цикла 450 не. Такой режим регенерации позволяет организовать обмен данными в синхронном режиме, не требует информации о состоянии микропроцессора и, главное, исключает простой микропроцессора. В режимах чтения и записи регенерация ячеек памяти, подключенных к выбранной строке, осуществляется автоматически. В режиме чтения на вход микросхем Wfc подается уровень логической единицы, а ь режиме записи — уровень логического нуля, г.осле чего на входы АО.. АН подается код столбца и с некоторой задержкой нулевой уровень на вход выбора столбца CAS. С помощью дешифратора столбцов определ. нная шина столбца через соответствующий ключ выборки подключается к шине данных, осуществляя запись или считывание информации в выбранной ячейке памяти. Электрическая схема модуля динамического ОЗУ изоб -ражена на рис. 2. Модуль включает в себя контроллер ОЗУ, реализованный на микросхемах DDI—DDI f, и основной блок ОЗУ объемом 64 Кбайта, на микросхемах DDI 2—DDI 9, перекрывающей адресное пространство 0U00H—FFFPH. Модуль динамического ОЗУ может быть использован как с процессорным модулем, так и совместно с дисплейным модулем. 11оскольку в процессорном модуле и в дисплейном модуле могут использоваться свои ПЗУ—ОЗУ, в модуле динамического ОЗУ имеется 8-входовая схема (DDL!) блокировки запросов обращения к модулю динамиче< кого ОЗУ. В частности, при работе модуля динамического ОЗУ только с микроЭВМ минимальной конфигурации, на входы блокировки следует подключить сигнал а выборки адресного пространства 0000Н—0FFFH, а на входы выборки кристалла микросхем ОЗУ процессорного модуля КР541РУ2 под 1ть сигналы логической единицы. В этом случае доступная область динамического ОЗУ будет составлять 60 Кбайт oi 1000Н до FFFFH. При подключении дисплейного модуля на входы блокировки подключают сигналы выборки адресного пространства 0000Н—OFFFFH, E000H—EFFFH и F000H— FFFFH. Работая с монитором в F800H—rFFFH, можно на входы выборки кристалла микросхем ПЗУ КР556РТ5 подать сигналы ло1 ической единицы, а со входа блокировки отключить сит налы выборки адресного пространства 000Н—0FFFH. В такой конфигурации доступная область динамического ОЗУ составит 56 Кбайт от 0000Н до 0FFFH. Сигналы выборки адресных пространств низкого уровня препятствуют формированию в триггере DDI сигнала длительностью, определяющей временной интервал обращения к ОЗУ. При этом модуль ОЗУ находится в режиме регенерации. Контроллер ОЗУ состоит из мультиплексора адреса, реализованного на микросхемах ПЗУ DD9—DD11, счетчика адреса регенер »ции на микросхемах D06 и DD7 (К155ИЕ5), схемы управления на регистре DD4 (К155ИР1), триггерах DDI и логических микросхемах DD2, DD3, DD5. При поступлении сигналов ЧТЗУ или ЗПЗУ по фронту импульса Ф2ТТЛ с помощью триггеров DDI на выходе схемы «2И-НЕ» (DD 2.1). Формируется импульс, длительность |