Юный техник - для умелых рук 1989-03, страница 12

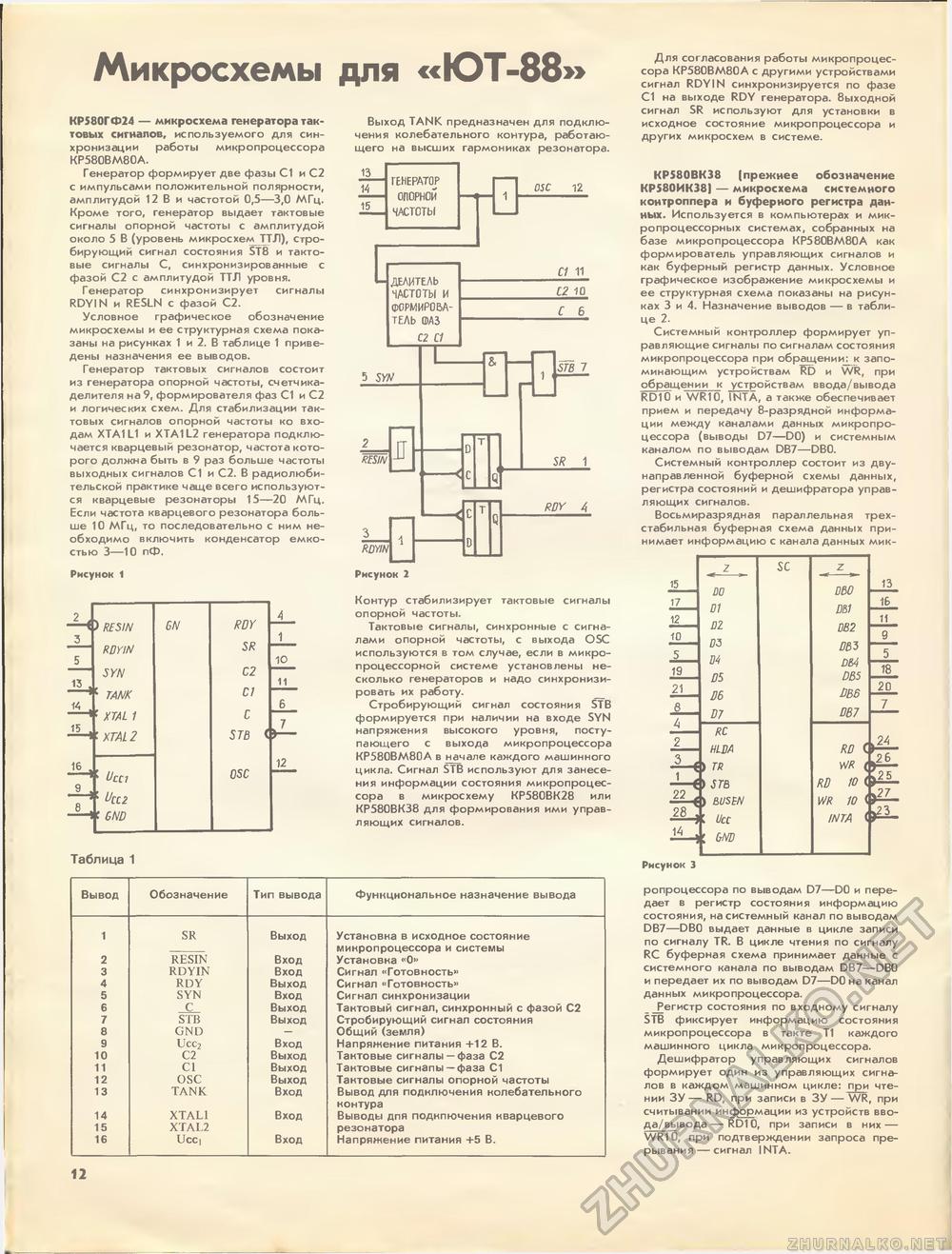

Микросхемы для с<ЮТ-88» КР580ГФ24 — микросхема генератора тактовых сигналов, используемого для синхронизации работы микропроцессора КР580ВМ80А. Генератор формирует две фазы С1 и С2 с импульсами положительной полярности, амплитудой 12 В и частотой 0,5—3,0 МГц. Кроме того, генератор выдает тактовые сигналы опорной частоты с амплитудой около 5 В (уровень микросхем ТТЛ), стро-бирующий сигнал состояния ST8 и тактовые сигналы С, синхронизированные с фазой С2 с амплитудой ТТЛ уровня. Генератор синхронизирует сигналы RDYIN и RESLN с фазой С2. Условное графическое обозначение микросхемы и ее структурная схема показаны на рисунках 1 и 2. В таблице 1 приведены назначения ее выводов. Генератор тактовых сигналов состоит из генератора опорной частоты, счетчика-делителя на 9, формирователя фаз С1 и С2 и логических схем. Для стабилизации тактовых сигналов опорной частоты ко входам XTA1L1 и XTA1L2 генератора подключается кварцевый резонатор, частота которого должна быть в 9 раз больше частоты выходных сигналов С1 и С2. В радиолюбительской практике чаще всего используются кварцевые резонаторы 15—20 МГц. Если частота кварцевого резонатора больше 10 МГц, то последовательно с ним необходимо включить конденсатор емкостью 3—10 пф. Рисунок 1 RESIN RDYIN 5YN TANK ХШ 1 XTAL2 Ucci UCC2 CND EN RDY SR C2 C1 С STB OSC Таблица 1 Выход TANK предназначен для подключения колебательного контура, работающего на высших гармониках резонатора. ГЕНЕРАТОР ОПОРНОЙ ЧАСТОТЫ ДЕЛИТЕЛЬ ЧАСТОТЫ И ФОРМИРОВАТЕЛЬ ШАЗ С2 С1 и 5 SYN 2_ шш л а и и ю с б SR 1 3_ RDYINl

Рисунок 2 Контур стабилизирует тактовые сигналы опорной частоты. Тактовые сигналы, синхронные с сигналами опорной частоты, с выхода OSC используются в том случае, если в микропроцессорной системе установлены несколько генераторов и надо синхронизировать их работу. Стробирующий сигнал состояния STB формируется при наличии на входе SYN напряжения высокого уровня, поступающего с выхода микропроцессора КР580ВМ80А в начале каждого машинного цикла. Сигнал ST используют для занесения информации состояния микропроцессора в микросхему КР580ВК28 или КР580ВК38 для формирования ими управляющих сигналов. Таблица 1

Для согласования работы микропроцессора КР580ВМ80А с другими устройствами сигнал RDYIN синхронизируется по фазе С1 на выходе RDY генератора, выходной сигнал 5R используют для установки в исходное состояние микропроцессора и других микросхем в системе. KPS80BK38 (прежнее обозначение КР580ИК38) — микросхема системного контроллера и буферного регистра данных. Используется в компьютерах и микропроцессорных системах, собранных на базе микропроцессора КР580ВМ80А как формирователь управляющих сигналов и как буферный регистр данных. Условное графическое изображение микросхемы и ее структурная схема показаны на рисунках 3 и 4. Назначение выводов — в таблице 2. Системный контроллер формирует управляющие сигналы по сигналам состояния микропроцессора при обращении: к запоминающим устройствам RD и WR, при обращении к устройствам ввода/вывода RD10 и WR10, INTA, а также обеспечивает прием и передачу 8-разрядной информации между каналами данных микропроцессора (выводы D7—D0) и системным каналом по выводам DB7—DB0. Системный контроллер состоит из двунаправленной буферной схемы данных, регистра состояний и дешифратора управляющих сигналов. Восьмиразрядная параллельная трех-стабильная буферная схема данных принимает информацию с канала данных мик- SC DB0 D51 DB2 т DR4 DB5 ЛВВ D6 7 RD т RD Ю WR 10 INTA 2А 25 £L <Ш- Рисунок 3 ропроцессора по выводам D7—D0 и передает в регистр состояния информацию состояния, несистемный канал по выводам DB7—DB0 выдает данные в цикле записи по сигналу TR. В цикле чтения по сигналу RC буферная схема принимает данные с системного канала по выводам DB7—DB0 и передает их по выводам D7—D0 на канал данных микропроцессора. _Регистр состояния по входному сигналу STB фиксирует информацию состояния микропроцессора в такте Т1 каждого машинного цикла микропроцессора. Дешифратор управляющих сигналов формирует один из управляющих сигналов в каждом машинном цикле: при чтении ЗУ — RD, при записи в ЗУ — WR, при считывании информации из устройств ввода/вывода— RD10, при записи в них — WR10, при подтверждении запроса прерывания— сигнал INTA. 000000000000000000000000000000000000000000000000000000000000000 |