Юный техник - для умелых рук 1989-03, страница 13

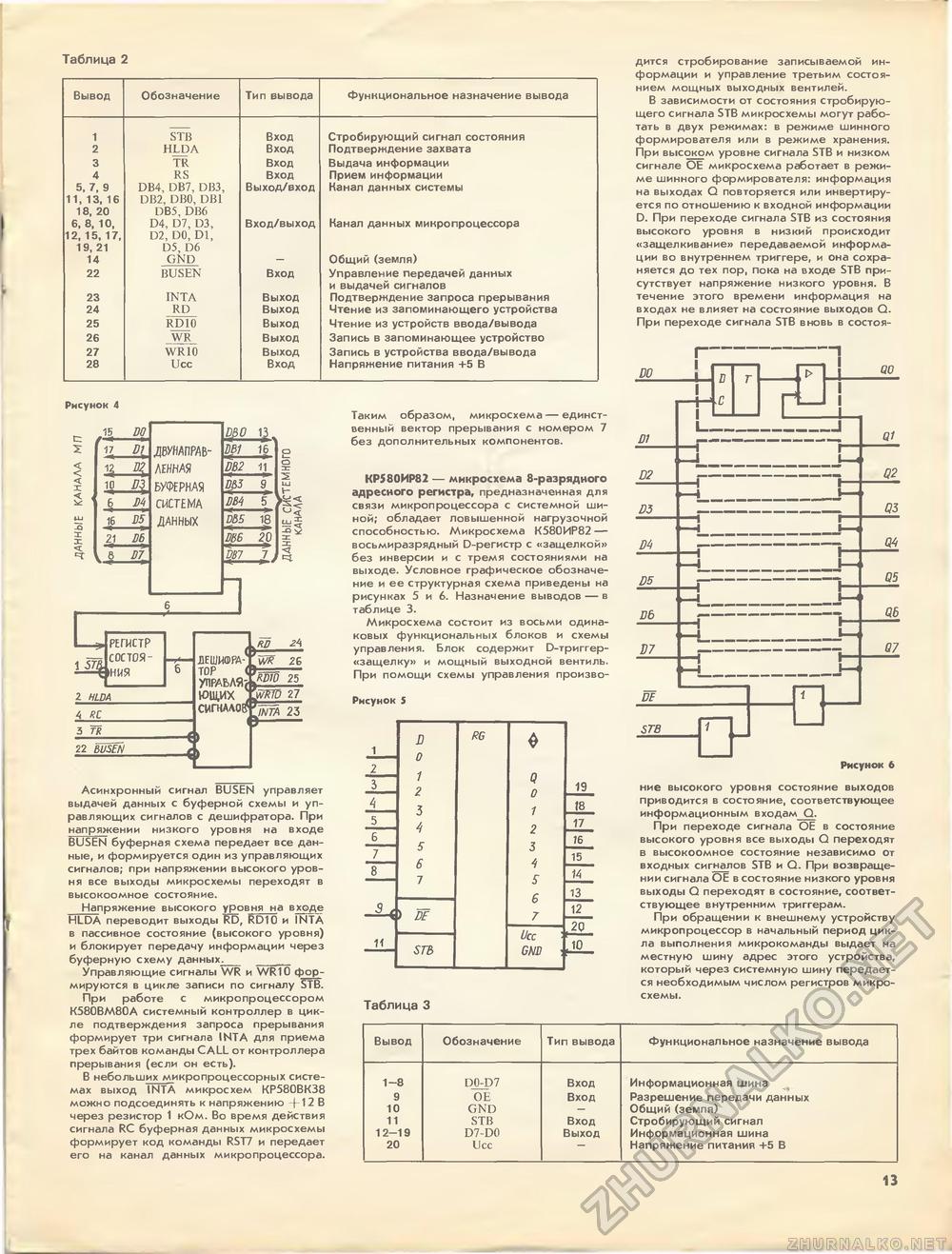

Таблица 2 Таблица 2

Рисунок 4 ■_DO ■_DO

ДВУНАПРАВЛЕННАЯ БУФЕРНАЯ CUCTt МА ЛАННЫХ

ш РЕГИСТР состояния ЛЕШИ® РА-ТОР ( УПРАЬЛЯ/jr' ЮШ.ИХ ) i СИГНАЛОВ т RD_гЛ ЯРЮ 25 ЩЮ 27 JNTA 23 Асинхронный сигнал BUSEN управляет Bi |дачей данных с буферной схемы и управляющих сигналов с дешифратора. При напряжении низкого уровня на входе BUSEN буферная схема передает все данные, и формируется один из управляющих сигналов; при напряжении высокого уровня все выходы микросхемы переходят в высокоомное состояние. Напряжение высокого уров ня на входе HLDA переводит выходы RD, RD10 и INTA в пассивное состояние (высокого уровня) и блокирует передачу информации через буферную схему данных_ Управляющие сигналы WR и WR10 формируются в цикле записи по сигналу STB. При работе с микропроцессором К580ьМ80А системный контроллер в цикле подтверждения запроса прерывания формирует три сигнала INTA для приема трех байтов команды CALL от контроллера прерывания (если он есть). В небольших микропроцессорных системах выход INTA микросхем КР580ВК38 д» ожно подсоединять к напряжению —|— 12 В через резистор 1 кОм. Во время действия сигнала RC буферная данных микросхемы формирует код команды RST7 и передает его на канал данных микропроцессора. Таким образом, микросхема — единственный вектор прерывания с номером 7 без дополнительных компонентов. КР580ИР82 — микросхема 8-разрядиого адресного регистра, предназначенная для связи микропроцессора с системной шиной; обладает повышенной нагрузочной способностью. Микросхема К580ИР82 — восьмиразрядный D-регистр с «защелкой» без инверсии и с тремя состояниями на выходе. Условное графическое обозначение и ее структурная схема приведены на рисунках 5 и 6. Назначение выводов — в таблице 3. Микросхема состоит из восьми одинаковых функциональных блоков и схемы управления. Блок содержит D-триггер-«защелку» и мощный выходной вентиль. При помощи схемы управления произво- Рисунок 5

Таблица 3 дится стробирование записываемой информации и управление третьим состоянием мощных выходных вентилей. В зависимости от состояния стробирую-щего сигнала STB микросхемы могут работать в двух режимах: в режиме шинного формирователя или в режиме хранения. При высоком уровне сигнала STB и низком сигнале ОЕ микросхема работает в режиме шинного формирователя: информация на выходах Q повторяется или инвертируется по отношению к входной информации D. При переходе сигнала STB из состояния высокого уровня в низкий происходит «защелкивание» передаваемой информации во внутреннем триггере, и она сохраняется до тех пор, пока на входе STB присутствует напряжение низкого уровня. В течение этого времени информация на входах не влияет на состояние выходов Q. При переходе сигнала STB вновь в состоя- D2 Е DA D5 Ив Ю □ ST8 1 F§ Q1 Q2 Q3 04 Q5 QB 07 Рисунок б ние высокого уровня состояние выходов приводится в состояние, соответствующее информационным входам Q. При переходе сигнала ОЕ в состояние высокого уровня все выходы G переходят в высокоомное состояние независимо от входных сигналов STB и Q При возвращении сигнала ОЕ в состояние низкого уровня выходы Q переходят в состояние, соответствующее внутренним триггерам. При обращении к внешнему устройству микропроцессор в начальный период цикла выполнения микрокоманды выдает на местную шину адрес этого устройства который через системную шину передает ся необходимым числом регистров микросхемы. Таблица 3

000000000000000000000000000000000000000000000000000000000000000 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||