Юный техник - для умелых рук 1989-05, страница 13

МИКРОСХЕМА' ДЛЯ «ЮТ-88» Микросхема К589Иь>12 — многорежимный восьмира грядчый универсальный буферный регистр. На одной или нескольких микросхемах этого типа можно реализовать ряд интерфейсных и вспомогательных устройств: регистры данных, буферные регистры со стробированиел данных, мультиплексоры, двунаправленные шин- входе MD логического 0 и для синхронной установки триггера запроса прерывания. Триггер запроса прерывания служит для выработки соответствующего сигнала в микропроцессорной системе. При установке система в исходное состояние низким уровнем сигнала ClR триггер запроса устанавличается в состояние запрета прерывания. Этс же сигнал заведует и разрешением прерывания. Считается, что Таблица 1 12 J5_J 1_ 6. Ю 13 Таблица 1

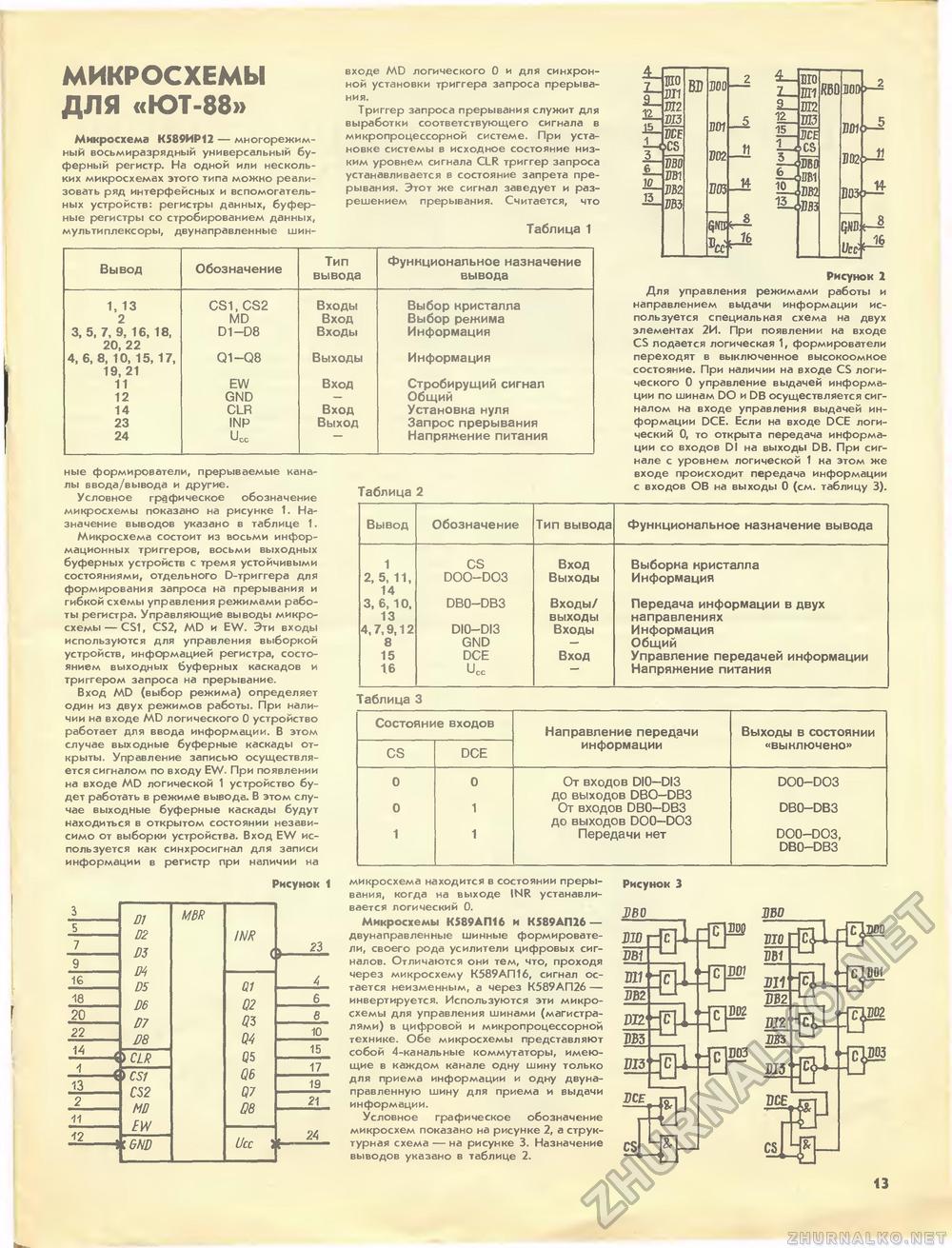

8 LM qimt-2- ные формирс вате и, прерываемые каналы свода вывода и другие. Условное графическое обозначение микросхемы показано на рисунке 1. Назначение выводов указано в таблице 1. Микро< хема состоит из восьми информационных триггеров, восьми выходных буферных устройств с тремя устойчивыми состояниями, отдельного D-триггера для формирования запроса на прерывания и гибкой схемы управ/.ения режимами работы регистра. Управляющие выводы микросхемы— CS1, CS2, MD и EvV. Эти входы используются для управления выборкой устройств, информацией регистра, состоянием выходных буферных каскадов и триггером запроса на прерывание. Вход MD (выбор режима) определяет один из двух режимов работы. При наличии на входе MD логического 0 устройство работает для ввода информации. В этом случае выходные буферные каскады открыты. Управление записью осуществляется сигналом по входу EW. При появлении на входе MD логической 1 устройство будет работать в режиме вывода. В этом случае выходные буферные каскады будут находиться в открытом состоянии незави симо от выборки устройства. Вход EW используется как синхросигнал для записи информации в регистр при наличии на Рисунок 1 Таблица 2 Рисунок 2 Для управления режимами pa6oibi и направлением выдачи информации используется специальная схема на двух элементах 2И. При появлении на входе CS подается логическая 1, формирователи переходят в выключенное высокоомное состояние. При наличии на входе CS логического 0 управление выдачей информации по шина.л DO и DB осуществляется сигналом на входе управления выдачей информации DCE. Если на входе DCE логический 0, то открыта передача информации со входов DI на выходы DB. При сигнале с уровнем ло! ической 1 на этом же входе происходит передача информации с входов ОВ на выходы 0 (см. таблицу 3). Таблица 2

Таблица 3 Таблица 3

микросхема находится в состоянии прерывания, когда на выходе INR устанавливается логический 0. Микросхемы KS89AI116 и К589АП26 — двун оправленные шинные формирователи, своего рода усилители цифровых сигналов Отличаются они тем, что, проходя через микросхему К589АП16, сигнал остается неизменным, а через К589АП26 — инвертируется, Используются эти микросхемы для управления шинами (магистралями) в цифровой и микропроцессорной технике. Обе микросхемы представляют собой 4-канальные коммутаторы, имеющие в каждом канале одну шину только для приема информации и одну двунаправленную шину для приема и выдачи информации. Условное графическое обозначение микросхем показано на рисунке 2, а структурная схема — на рисунке 3. Назначение выводов указано в таблице 2. 13 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||